团队处理器系列(0x02):木心处理器核-需求设计

前言

我是在大三下学期的时候(即2016年的夏天)第一次听到了RISC-V这个词,那会儿我舍友刚好参加了学院组织的《计算机体系结构》试点班,而他们的任务就是要基于RISC-V指令集去设计一款简单的软核CPU,当时我只知道它是由伯克利大学推出的开源RISC指令集,觉得跟我们普通班学习所要用到的MIPS指令集类似,所以就没有太放在心上。可是令人没有想到的是,经过短短几年的发展,RISC-V指令集已经得到了全世界众多互联网和半导体巨头的支持,而且有越来越多的研究机构和初创公司开始基于它来设计自己的专有处理器,我认为目前的RISC-V就像早期的Linux内核,虽然功能和性能还非常有限,但是借助开源协作的力量,我相信总有一天RISC-V也能在某些领域迎来一场足以改变旧有格局的革命。因此为了不被即将到来的新时代所抛弃,作为一名业余硬件爱好者,我觉得自己还是很有必要好好学习一下RISC-V指令集的,没准以后有机会还能为国产自主可控处理器的设计和研发贡献自己的一份力量!

古人曾经说过:纸上得来终觉浅,绝知此事要躬行,既然自己决定要学习RISC-V,那就必须亲身实践才能搞明白,而对于这种处于计算机体系结构底层的项目来说,没有什么能够比自己从零实现一遍更好的方法了,于是抱着这种想法我开始在网上搜集资料,结果比较令人失望,虽说国外与RISC-V相关的开源项目有不少,但是其中很多都是用Chisel这种高级硬件构建语言来实现的,学习门槛非常高,再加上为了追求整体的性能,一些CPU的系统架构设计得非常复杂(如采用五级以上流水线、多核处理、乱序执行等),初学者想入门非常困难。所以经过深思熟虑后,我决定从零编写一款系统架构足够精简、代码足够清晰、封装足够优秀的开源处理器项目,希望它能像从众多微控制器中脱颖而出的Arduino一样,让更多的硬件爱好者可以快速上手体验,并基于此开发很多有意思的应用,未来在软硬件生态环境的互相促进下,也许会有更多的人喜欢上CPU开发并愿意花时间去钻研,如果真的能够做到如此,我也就心满意足了。

内容

任务进度

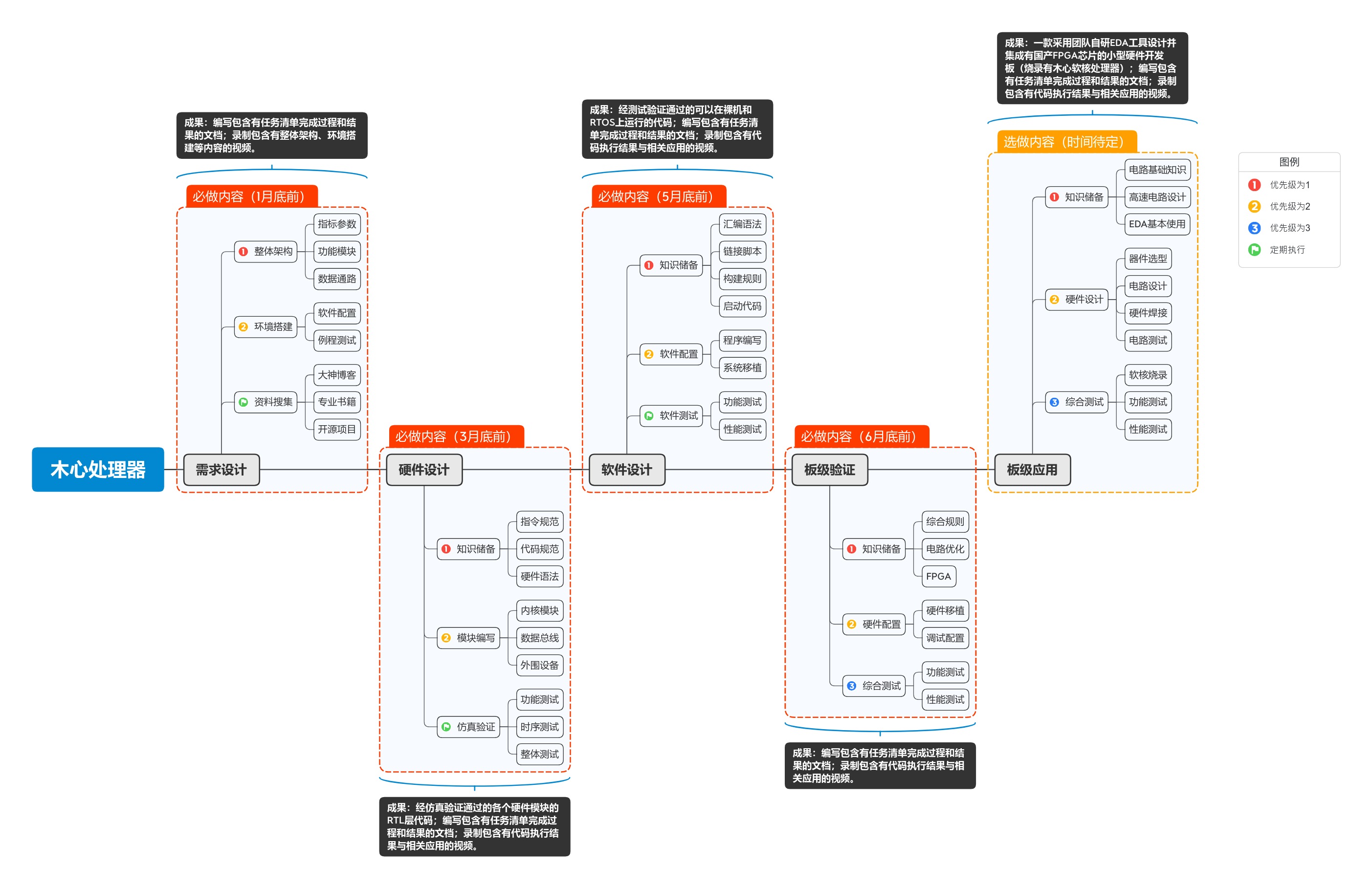

如下图所示,根据木心开源处理器项目所涉及的技术要点,我将其第一版的开发任务总共划分为了5个阶段,分别为需求设计、硬件设计、软件设计、板级验证和板级应用,其中考虑到自己是第一次从零开始编写处理器,应该把更多的注意力放在代码的实现和调试上,所以板级应用这个阶段我将其设置成了选做,如果后期有时间的话,我还是希望自己能够将木心处理器封装到自己设计的开发板上的,好了废话不多说了,接下来简单介绍一下前4个阶段所必须要完成的任务内容。

首先是需求设计阶段,这个阶段主要是根据相关专业书籍和RISC-V指令集手册,确定木心处理器的整体架构,并完成软件开发环境的配置;紧接着是硬件设计阶段,这一步需要基于需求设计阶段所确定的系统架构,完成处理器功能模块与数据通路等核心硬件代码的编写和测试工作;接下来是软件设计阶段,在这期间需要完成软件底层(汇编文件、启动文件、链接脚本等)配置以及RTOS系统移植,从而确保木心处理器最终能够分别在裸机和RTOS环境下运行C语言程序;最后是板级验证阶段,顾名思义就是将软硬件代码烧录到FPGA开发板上,然后在物理端验证处理器的功能和性能等指标是否满足项目要求。

整体架构

指标参数

基于为了能够让初学者们更好入门的核心目标,我将第一版木心处理器的内部开发代号命名为TC-L1(TreeCore Learn 1),即木心学习专用处理器第一版的英文简写,它是一款由处理器核、数据总线和外围设备所组成的SoC,无论是系统的核心与外围功能模块,还是指令执行所依托的数据通路在设计与实现阶段均追求极致的精简,只保留能够维持系统正常运行的最小环境,所以你可以把它看成是处理器领域的一个最小系统。注意:后文所有【处理器】特指的是SoC,而【处理器核】则指的是SoC中能够执行具体指令的硬件逻辑单元。

木心TC-L1处理器的特性如下所示:

- 处理器核支持最基础的RV32I指令集,且能通过RISC-V指令集兼容性测试;

- 处理器核采用最经典的的五级流水线结构(即取指、译码、执行、访存和写回),且所有指令均是单发射顺序执行的,即系统架构设计满足Unix内核的K.I.S.S.准则;

- 处理器核设计有标准的JTAG调试接口,可通过OpenOCD实现系统的在线调试与升级;

- 处理器核设计有专用的数据总线接口,可通过数据总线与外围设备(目前设计有GPIO、SPI、UART等)进行单向或双向通信;

- 处理器核能够在裸机和RTOS环境下运行C语言程序;

- 处理器可通过参数进行配置,方便移植到各种FPGA平台(在逻辑资源允许的情况下)。

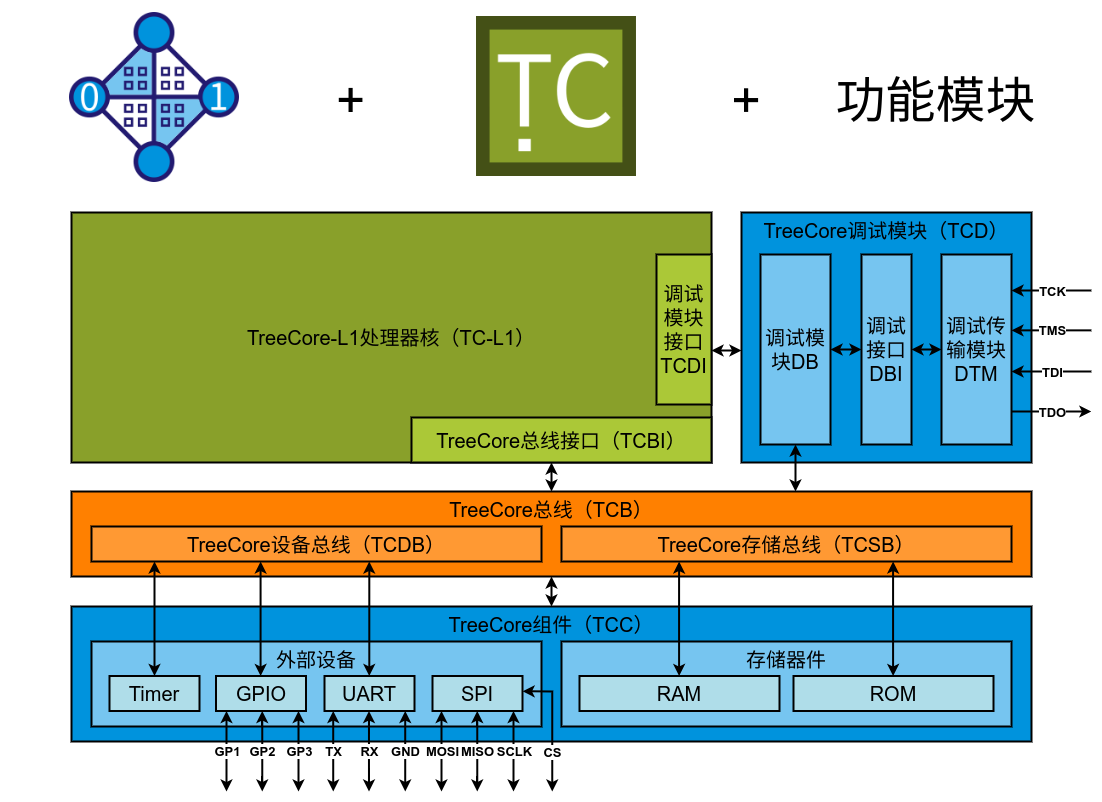

功能模块

如下图所示,TC-L1处理器的功能模块主要分为4大部分,分别为TC-L1处理器核、TCD调试模块、TCB数据总线以及TCC外部组件,其中处理器核毫无疑问是整个SoC里面最重要的一个模块,它主要负责处理经过软件编译生成的底层指令,并可通过总线接口与其他模块进行数据交互;调试模块则扮演的是辅助角色,用于在编写处理器的过程中提供快速定位系统Bug的能力;接下来的数据总线模块,其功能就好比是现实世界中的桥梁,可建立起处理器内部各模块之间的数据通路,便于实现数据的快速访问;而最后的外部组件模块则包含外部设备和存储器件共两个子模块,其中外部设备模块可实现处理器核与外部标准设备进行数据通信,而存储器件模块则主要用于存储维持处理器运行的各种指令和数据。

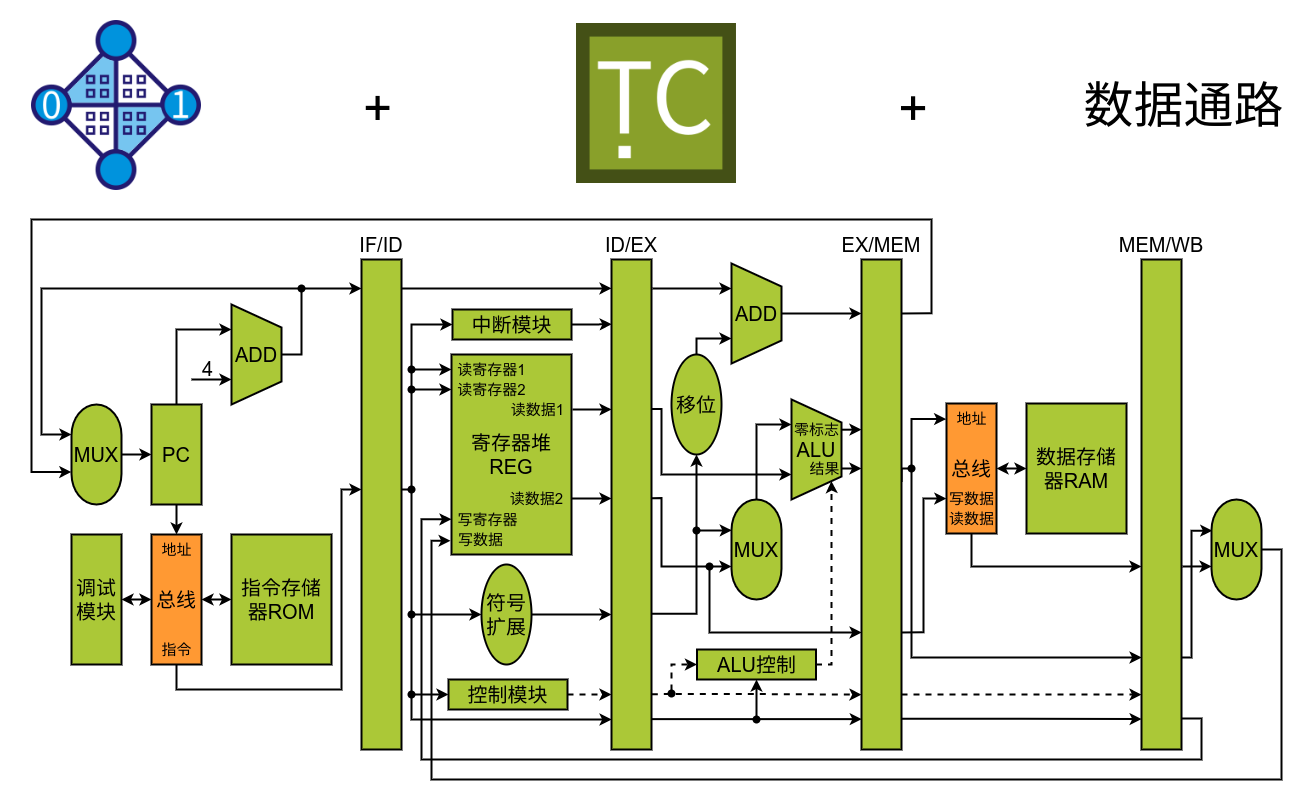

数据通路

在介绍完TC-L1处理器的各种功能模块之后,接下来让我们简单了解一下其内部的数据通路具体是什么样子的。如下图所示,TC-L1处理器核的数据通路采用经典的五级流水线结构,整条流水线由4个流水线寄存器(图中用细长条矩形标识)加以划分开来,其中最左侧的区域为取指阶段,此时处理器会根据PC寄存器中的地址,从指令存储器中获取需要执行的指令,并将其加载到IF/ID流水线寄存器中,以便在下一个时钟边沿到来时能够将数据传递给下一阶段;取指之后自然是译码阶段,此时处理器会根据组合逻辑译码后的结果,初始化核心控制逻辑,并依据指令的具体内容,执行内部中断、读寄存器或符号扩展等操作。

之后3个阶段依次分别为执行、访存和写回,其中在执行阶段,处理器会使用ALU对指令数据进行运算,并将最终运算得到的结果保存到流水线寄存器EX/MEM中以供后面使用;而对于访存阶段来说,此时处理器在控制信号的约束下,会对数据存储器进行读写操作,如果指令是读数据的话,则类似需要将获取到的数据保存到流水线寄存器MEM/WB中以供后面使用;流水线的最后是写回阶段,这一步其实执行逻辑很简单,就是将上一阶段读出的数据或在执行阶段得到的运算结果写回到译码阶段中的寄存器堆中,为之后指令的执行奠定数据基础。

环境搭建

软件配置

在上一篇《团队处理器系列(0x01):软件安装与配置》文章中,我曾经详细地介绍了如何在Ubuntu系统上安装ModelSim这款CPU仿真利器,不过由于它本身是付费软件,配置过程(大家都懂的)对于新手来说比较复杂,再加上本项目对波形仿真的功能与性能没有太高的要求,所以这次我决定采用免费、开源的iverilog+gtkwave组合来替代之前的ModelSim。在类Debian系统(如Ubuntu)上的安装方法如下:

1

2

3$> sudo apt update

$> sudo apt install iverilog

$> sudo apt install gtkware例程测试

在打开的命令行终端中依次输入以下命令:

1

2

3

4

5$> mkdir ~/Workspaces

$> cd ~/Workspaces

$> git clone git@github.com:microdynamics-cpu/tree_core_cpu.git

$> cd tree_core_cpu/env

$> ./hello_world_tb.sh如果正常的话,此时应该能看到如下界面:

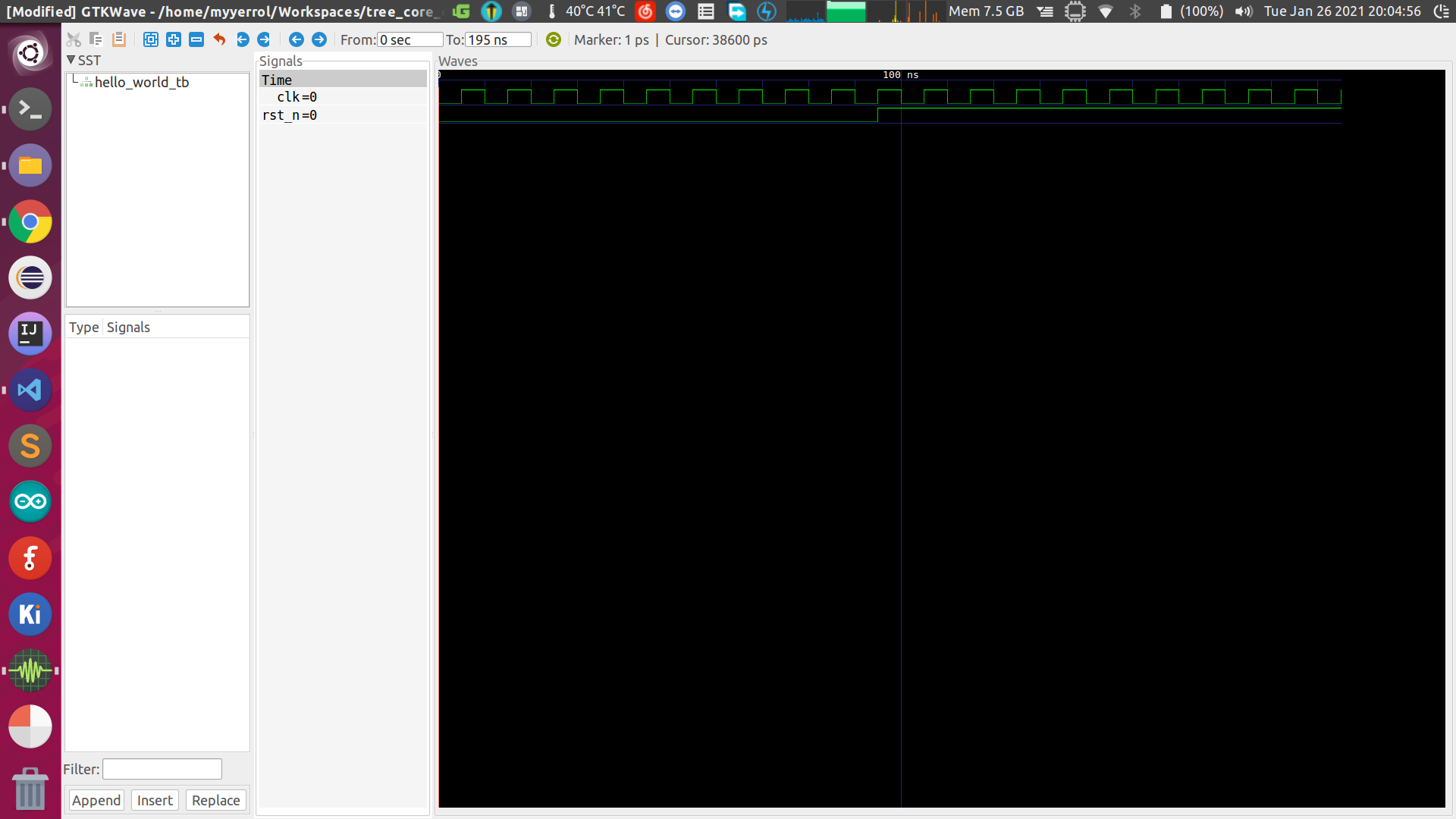

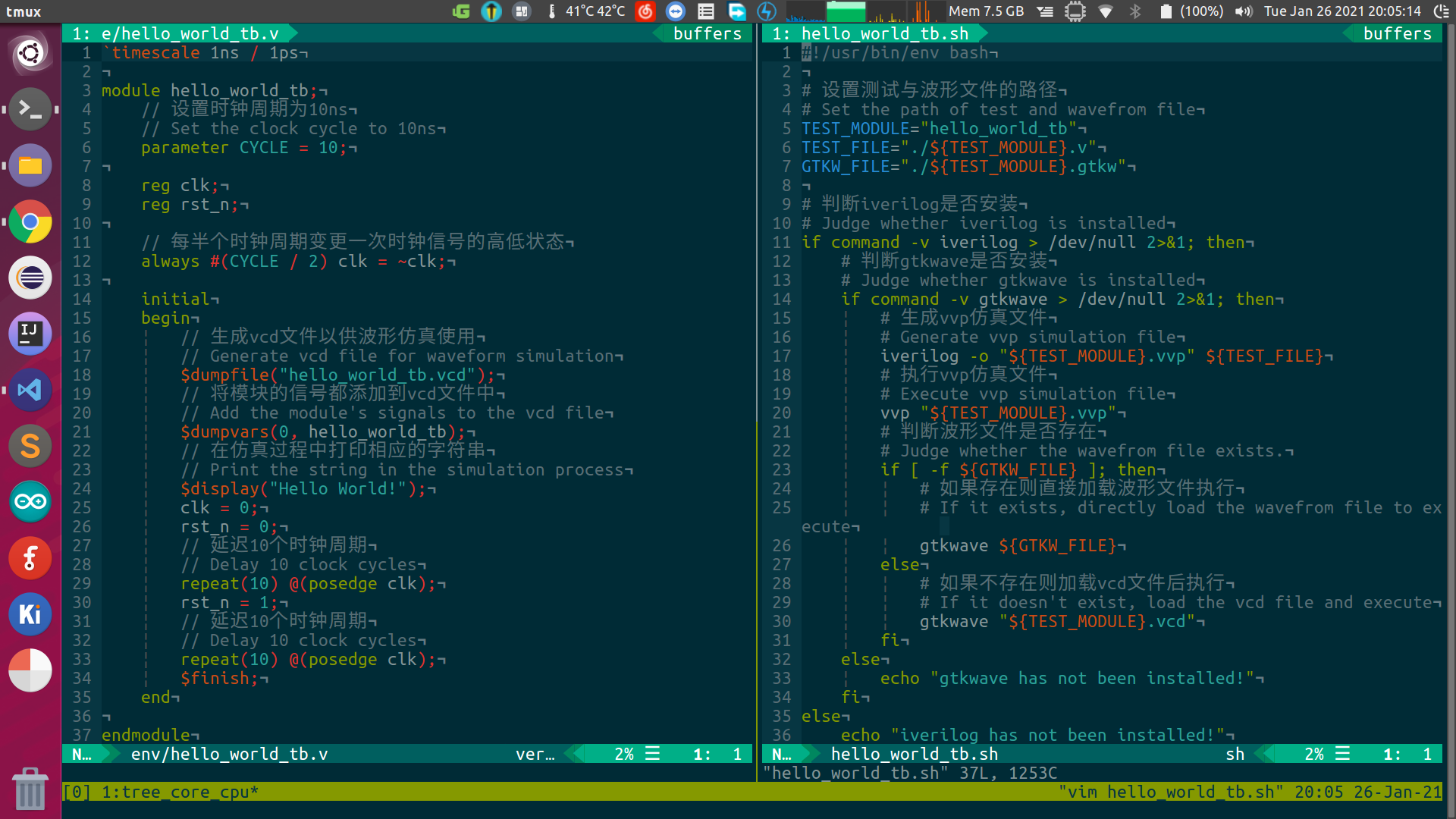

以上是我编写的一个Verilog版的Hello World!程序的波形仿真结果,从图中可以看到测试模块的逻辑非常简单,只有两个信号,分别为时钟信号clk和复位型号rst_n,其中时钟信号每半个周期改变一次高低电平状态,而复位信号rst_n则是在10个周期后才由低电平变为高电平,之后系统在保持其高电平状态的情况下再运行10个周期,整个仿真流程便结束了。虽然这个例程的逻辑功能非常简单,但是却还原了一个最小的硬件仿真流程,能够让初学者们对接下来的硬件开发先有一个最基本的认识。

此外,我编写该测试例程的另一目的是为了实现一套最简单的RTL代码自动化编译与波形仿真的模板,如下图所示,用户只需在Testbench文件中添加两行$dumpfile配置函数,并Shell脚本中将测试模块的名称修改为实际Testbench文件的名字,便可通过在终端中执行该脚本以完成对RTL代码的自动化编译与加载波形仿真的工作,可以说有效地提高了硬件代码的验证效率,后期木心项目也会采用该模板来组织工程内的RTL代码。至于测试文件与脚本文件的具体内容,这里由于篇幅原因就不再过多赘述了,感兴趣的同学可以自行研究。

资料搜集

专业书籍

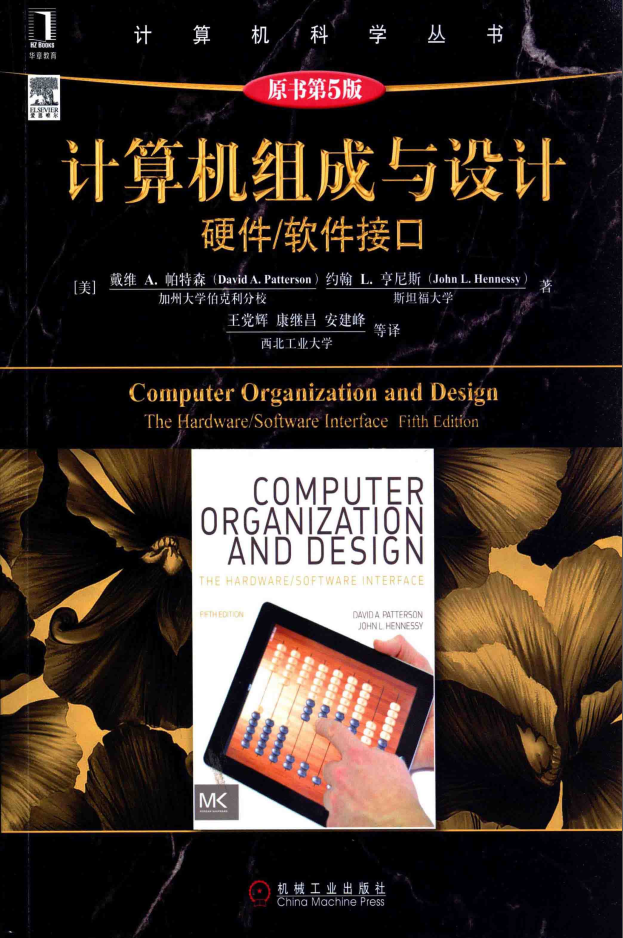

下面这本书绝对称得上是计算机体系结构领域里最有名的著作之一,因为它是由RISC架构的奠基者帕特森教授和亨尼斯教授合作编写的(两位宗师级大佬荣获了2017年ACM图灵奖),书中详细介绍了计算机体系结构的相关基础知识,并以MIPS指令集为例给出了一款经典RISC处理器的设计方法,内容质量非常高。这里推荐给大家一方面是因为第一版木心处理器采用的就是这本书中所介绍的经典五级流水线架构,这样后期大家学习起来会比较容易,二是这本书的译者之一是大学本科给我们上过课且带过我毕设的老师,出于对母校的感情,就允许我任性地自荐一下吧。

这本指南是由中科院计算所包云岗老师团队负责翻译的,原作为帕特森教授(RISC架构发明者)和沃特曼博士(SiFive创始人)合作编写的《The RISC-V Reader》,这本书给出了所有官方已定义的RISC-V指令集格式,并按照章节对RISC-V基础整数指令子集RVI、乘除法指令子集RVM、浮点指令子集RVF和RVD、原子操作指令子集RVA,以及其他可选的扩展子集进行了详细介绍,可以说是目前关于RISC-V指令集最权威且最全面的资料。在开始学习或动手实践前,强烈建议各位好好研究一下这本书,绝对受益匪浅。

开源项目

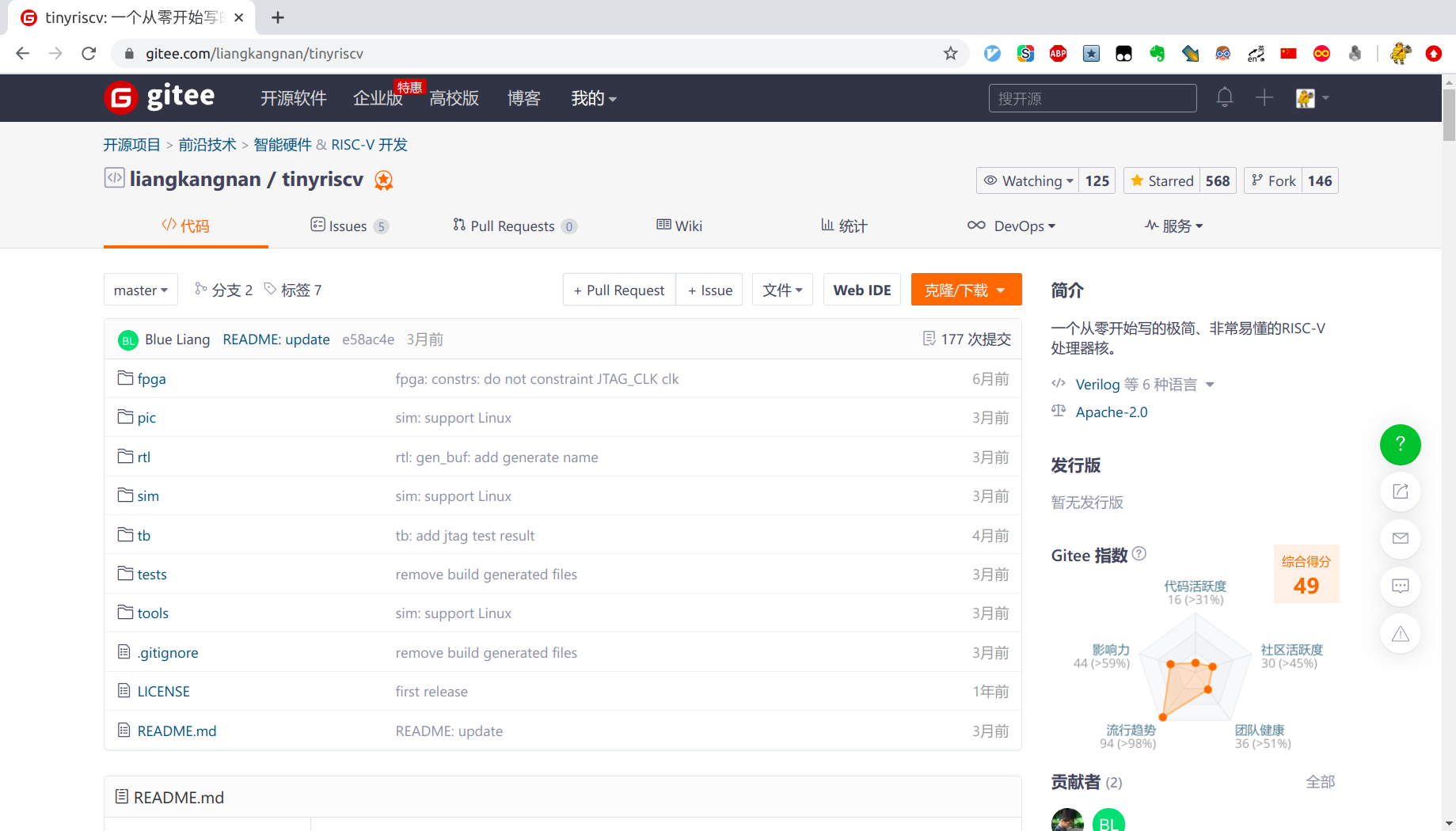

目前国内与RISC-V相关的开源项目屈指可数,其中我觉得最适合小白入门学习的是下图中的这个tinyriscv项目,推荐理由主要是因为这款处理器不仅系统架构设计得非常简单,而且代码书写风格也非常规范,初学者只需要花很短的时间就能弄明白处理器执行指令的整个流程。除此之外,作者还编写了与本项目相配套的设计文档——《从零开始写RISC-V处理器》,里面详细地介绍了处理器的硬件实现、外部调试、软件测试等内容,文章总体质量非常高,后期木心项目也会在一定程度上借鉴tinyriscv项目的某些设计理念,当然无论最终本项目的完成情况如何,这里我都要先给tinyriscv项目的作者点一个大大的赞。

总结

从大学选择硬件作为自己本科的学习方向开始,我就一直坚信它是支撑整个信息时代最关键的组件,试想一下倘若没有硬件所搭建的基础环境,那面向用户的高级操作系统也将不复存在,而如果没有了操作系统作为硬件和软件间的桥梁,那可以毫不夸张的说,当下信息时代的所有产物(互联网、大数据、AI等)都不可能会出现。处理器作为硬件的中枢神经,其重要性自然不言而喻,如果把整个信息产业比喻成一棵树木的话,那我认为处理器就是这棵树的精神核心(简称木心,没错本项目的命名便是由此而来的),只有一棵树的木心足够稳定和强大,那它才能不断成长为根系错综复杂、枝叶繁盛茂密的参天大树,从而有力量抵抗外部各种恶劣环境而长久屹立不倒,处理器亦是如此。

前段时间我在知乎上看到了包云岗老师所写的有关国科大“一生一芯”计划的故事,相较于本科生能够带着自己设计的芯片毕业,我觉得该计划更大的意义在于:它打破了传统芯片教学无法在物理层面实践的壁垒,让更多的学生看到了独自设计芯片的可能性,如果能有更多的人喜欢处理器设计并愿意投入到其中,那未来国内芯片设计人才短缺的问题将会得到不断改善,中国也就有机会逐渐摆脱被发达国家卡脖子的窘境,于是借着“一生一芯”计划带给自己的启示,我决定启动木心项目,希望除了CS专业的大学生之外,普通的爱好者们也能转变对芯片设计的态度,并愿意尝试去学习底层技术,假以时日,星星之火也许真的可以燎原。

最后,感慨一下:在当前这个利益至上的时代,情怀是肯定敌不过生活的,但是人的生命只有一次,能够在有限的生命里去做一件有意义且难度大的事情,就算最后没有达到自己当初所设立的目标,我觉得这份经历本身也足以配得上成功二字!

文章作者: myyerrol

最后更新:

原始链接: https://myyerrol.xyz/zh-cn/2021/02/06/team_cpu_2_treecore_design/

版权说明: 本博客所有文章除特别声明外,均采用 BY-NC-SA 4.0许可协议 。获得许可后,要求转载时注明文章出处和网站链接,谢谢!